# **TAU 2016**

Debjit Sinha & Qiuyang Wu

Hilton Sonoma Wine Country, Santa Rosa, CA March 10-11, 2016 www.tauworkshop.com

### TAU trivia

- Longest title ACM International Workshop on <u>Timing Issues</u> in the Specification and Synthesis of Digital Systems

- Shortest nickname Τ

- Started in 1989 @ Univ. of California at Berkeley [40 attendees]

- General chair Rick McGeer, TPC chair Bob Brayton

- TAU 2016 23<sup>rd</sup> in series

- Evolved from a pure digital timing workshop

- Analog and mixed signal circuits

- Power analysis, optimization

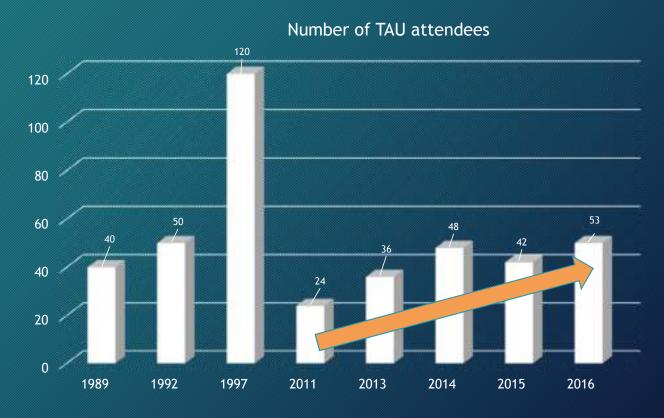

## TAU evolution - Few data points

- 40+ attendees on average

- Growth in the past 5 years

- Industry dominated

- < 15% academia</li>

- Timing contest since 2013

- Send your problems

- Participate [Organize]

### TAU 2016 organization

#### Organizing committee

- General chair: Debjit Sinha (IBM)

- TPC chair: Qiuyang Wu (Synopsys)

- Contest chair: Jin Hu (IBM)

- Past general chair: Igor Keller (Cadence)

#### Contest committee

- Chen Xi (Synopsys)

- Jin Hu (IBM) Chair

- Song Chen (Synopsys)

- Xin Zhao (IBM)

#### Technical program committee (TPC)

- Oscar Ou (MediaTek)

- Hong Li (Xilinx)

- João Geada (CLK DA)

- Jonathan Bishop (Mentor Graphics)

- Ramesh KS (Intel)

- Ken Stevens (University of Utah)

- Masanori Hashimoto (Osaka University)

- Peng Li (Texas A&M University)

- Praveen Ghanta (Cadence)

- Qiuyang Wu (Synopsys) Chair

- Richard Phillips (nVidia)

- Subra Sripada (Synopsys)

- Tom Spyrou (Altera/Intel)

- Vladimir Zolotov (IBM)

- Xin Li (Carnegie Mellon University)

#### ACM & Hilton

Diana Brantuas, Farrah Khan, Stephanie Sabal (ACM)

Tessa Borquez, Danni Randolph (Hilton)

### Technical program

- 53+ attendees

- EDA, design houses, foundries, academia

- 17 companies Arcadia, ARM, Broadcom, Cadence, Clariphy, ClkDA, HHMI, IBM, Intel/Altera, MediaTek, Mentor Graphics, NVIDIA, Oracle, Qualcomm, Synopsys, TSMC, Xilinx

- 6 universities UCSD, UIUC, Univ. of Utah, Kyoto Institute of Technology, Osaka University, Kyoto University

- 4 special sessions Keynotes, contest talk etc.

- 5 technical sessions 20 papers [including 3 invited talks]

- 2 panels

### Keynotes, special session & invited talks

#### Invited talks

- Intel High Performance Latch Based Design: Optimization and Timing Verification Challenges

- Altera/Intel The Stratix 10 Hyperflex Architecture and its impact on Timing Analysis

- Xilinx A Practical Approach to Clock Skew Optimization for FPGAs

### Logistics

- Complimentary Wi-Fi (in meeting room [passcode: tau] and guest room)

- Complimentary parking

- Complimentary cheese & wine tasting at lounge every evening after 5PM

- Reception (dinner buffer): today 7-9 PM @ Sonoma Ballroom

- Speakers

- Upload your charts to TAU laptop before session (breakfast/break)

- Unless you have emailed your latest version to Qiuyang

- Strictly 12 mins + 3 mins Q&A for most talks

- Inform TPC chair if you do not want your charts to be uploaded to the website

### TAU 2016 acknowledgments

- Sponsors Thank You

- ACM

- Cadence

- IBM

- Synopsys

- You all

- Participate TPC, contest committee

- Suggest

- Contribute

- Spread the word ...

- Enjoy these two days

- Mini vacation at Sonoma Wine Country

- Avoid laptop usage (if possible)

- Please <u>switch-off or mute</u> cell-phones

- Event pics will be posted online www.tauworkshop.com