# Highly-dense Mixed Grained Reconfigurable Architecture with Via-switch

Ryutaro Doi<sup>1,6</sup> Junshi Hotate<sup>2,6</sup> Takashi Kishimoto<sup>2,6</sup> Toshiki Higashi<sup>2,6</sup> Hiroyuki Ochi<sup>2,6</sup> Munehiro Tada<sup>3,6</sup> Tadahiko Sugibayashi<sup>3,6</sup> Kazutoshi Wakabayashi<sup>3,6</sup> Hidetoshi Onodera<sup>4,6</sup> Yukio Mitsuyama<sup>5,6</sup> Masanori Hashimoto<sup>1,6</sup>

<sup>1</sup>Osaka University <sup>2</sup>Ritsumeikan University <sup>3</sup>NEC <sup>4</sup>Kyoto University

<sup>5</sup>Kochi University of Technology <sup>6</sup>JST, CREST

nanocrest@gmail.com

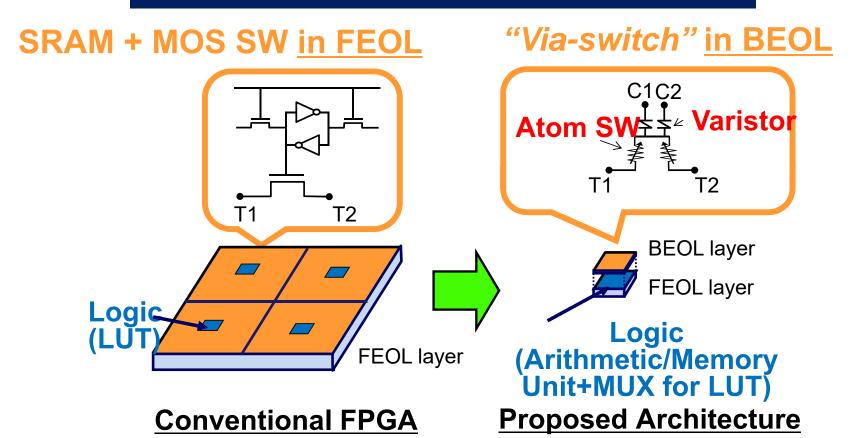

#### Contribution

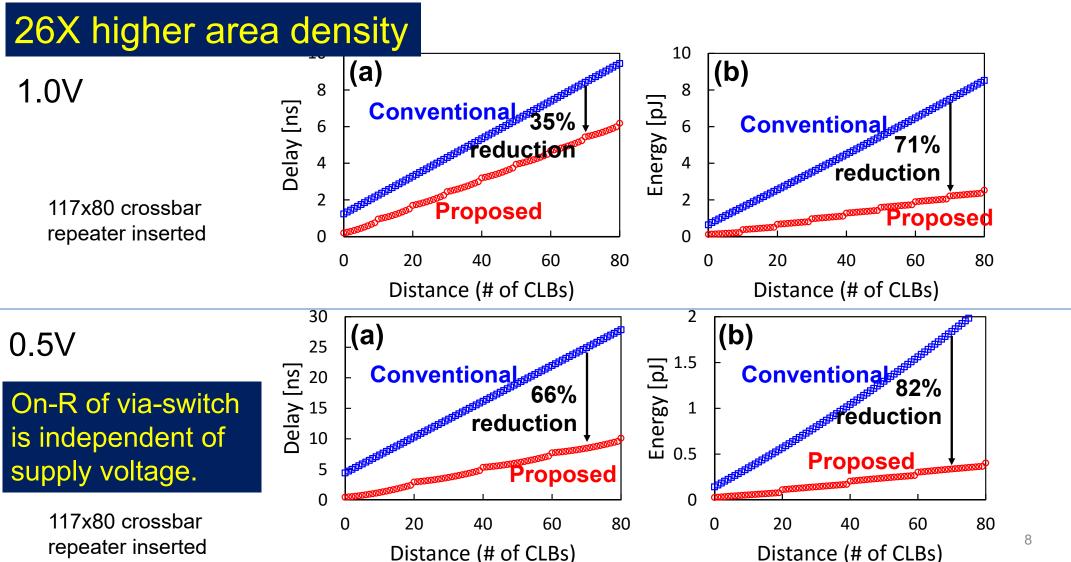

26X higher density 66% smaller interconnect delay at 0.5V

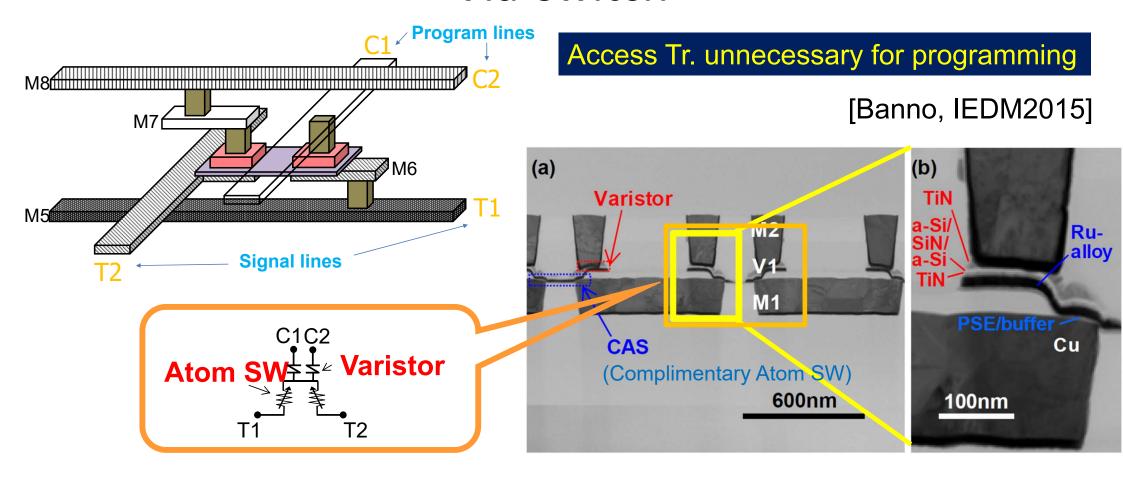

#### Via-switch

Atom SW: Electrochemical nonvolatile R-change device On-R can be reduced to  $200\Omega$ .

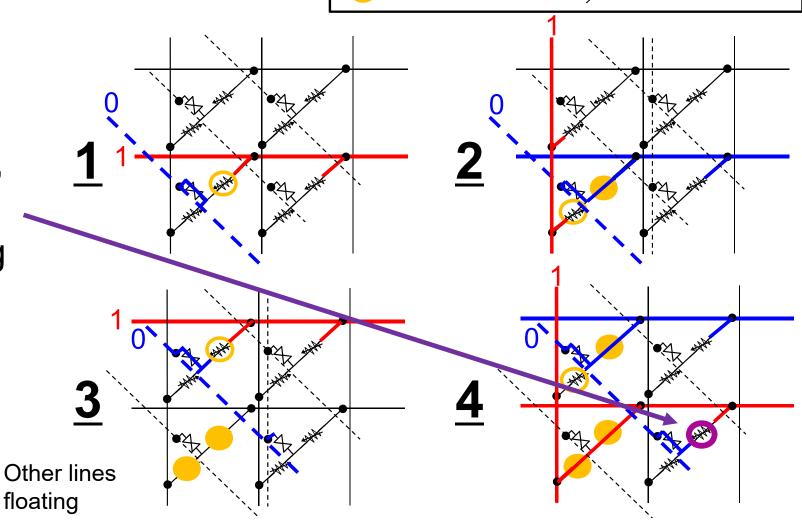

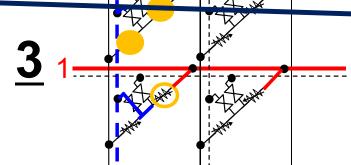

## Why two program lines?

Atom SW under intentional programming

Atom SW under unintentional programming

On-state Atom SW 🦟 Off-state Atom SW

With a single program line, unintentional programming will happen.

## Why two program lines?

Atom SW under programming

On-state atom SW

Off-state atom SW

With two program lines, unintentional programming will not happen.

Multiple-ON in a column enables multiple fanouts.

> Other lines floating

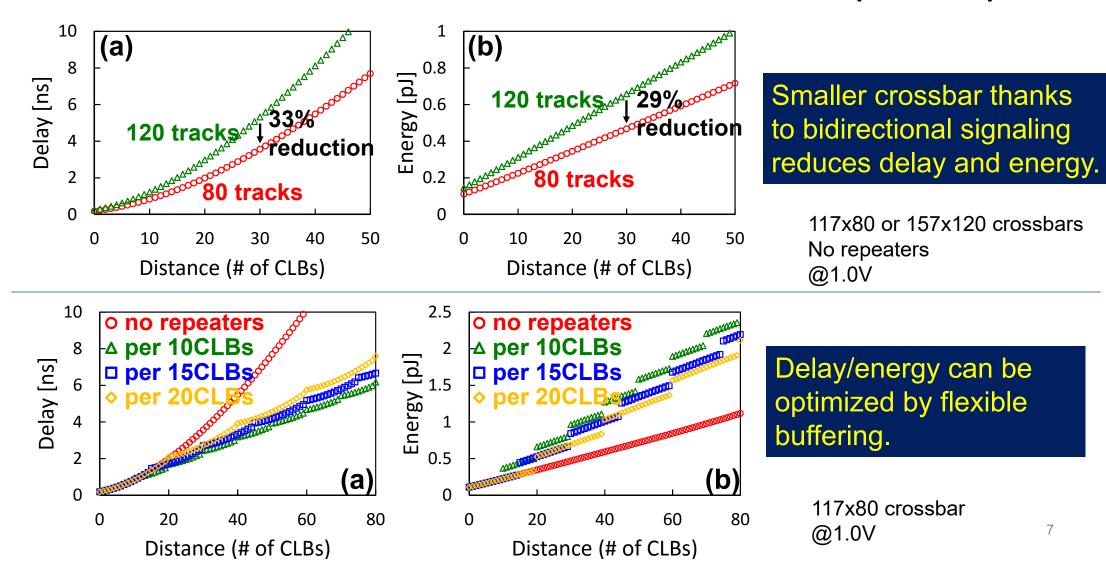

## Interconnect Performance Evaluation (65nm)

## Comparison w/ SRAM-based FPGA (TMG+SRAM crossbar)

#### Conclusion

- Proposed a highly-dense reconfigurable architecture that exploits via-switch.

- 26X higher density

- Interconnection delay is reduced by 35% (1.0V) and 66% (0.5V)

- Interconnection energy is reduced by 71% (1.0V) and 82% (0.5V)

- Future works

- Import long wire interconnection

- Application mapping and performance evaluation