## Accurate Timing Updates for Circuit Optimization without Explicit Parasitic Data

Ruiming Li, Rajendran Panda, Tong Xiao, Ted Hong, Xiaomi Mao Oracle Corporation, USA

#### Outline

- Motivation

- New approach to update timing in circuit optimization without explicit parasitic data.

- Results and Conclusion

#### Motivation

- Our in-house tool fixing timing violations

- Need quick timing estimation with good accuracy

- Timing data from reference timer as a starting point

- Need light weight without using netlist parasitic

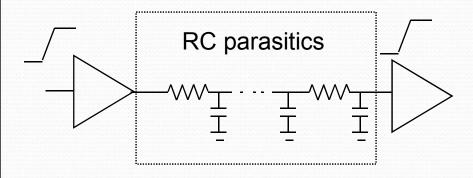

## Method to estimate timing without parasitics

Traditional delay/slew estimation

• Compute delay/slew by: SPICE, AWE, RICE, PRIMA, D<sub>2</sub>M, S<sub>2</sub>M, etc.

Our estimation flow

- Compute new delay/slew after gate sizing by: D2M, S2M.

- Memory saved from parasitics. Runtime saved from parasitic reduction

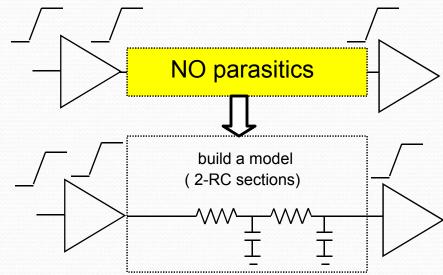

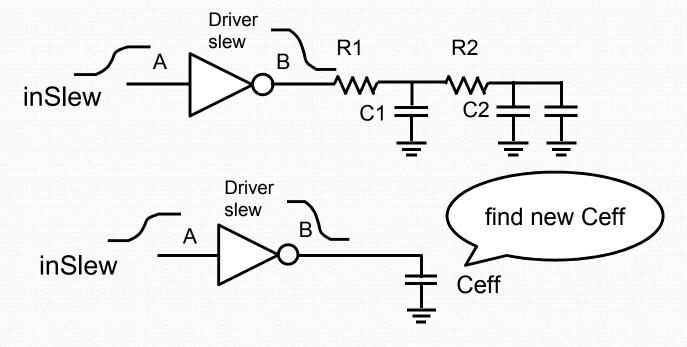

#### How to construct net model?

• Known data before sizing gates: **tr**, **d**, **s**, **C**total, **C**L

Figure 2: Net model computation

- First, find two moments **m1** and **m2** from **tr, d, s**

- Compute R1 and R2 from m1 and m2

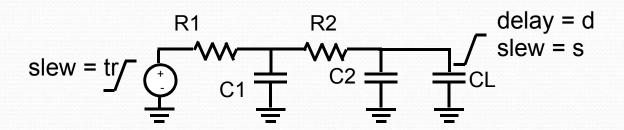

## Net Model: Leverage D2M and S2M reversely

D2M (Ref [5])

• Step input:

$$Delay_{D2M} = \frac{m_1^2}{\sqrt{m_2}} \ln 2$$

. Ramp input:  $Delay_{D2M_{ramp}} = -(1-\alpha)m_1 + \alpha * Delay_{D2M}$  (1)

$$\alpha = \left( \frac{2 m_2 - m_1^2}{2 m_2 - m_1^2 + tr^2 / 12} \right)^{\frac{5}{2}}$$

• S2M (Ref [7])

• Step input:

$$Slew_{D2M} = \frac{\sqrt{-m_1}}{\sqrt[4]{m_2}} \ln 9\sqrt{2m_2 - {m_1}^2}$$

. Ramp input:

$$Slew_{D2M_{ramp}} = \sqrt{Slew_{D2M}^2 + tr^2}$$

(2)

### Net Model: Compute moments m1 and m2

• The relationships between **m1**, **m2** and **d**, **s** and **tr** are

$$\begin{cases} -(1-\alpha)m_1 + \alpha * \frac{m_1^2}{\sqrt{m_2}} \ln 2 = d \\ \frac{-m_1}{\sqrt{m_2}} (\ln 9)^2 (2m_2 - m_1^2) + tr^2 = s^2 \end{cases}$$

(3)

- Solving (3) iteratively w. r. t.  $\alpha$  (initial  $\alpha$  = 1)

- For fixed lpha , (3) reduces to cubic equation

$$a_3 m_1^3 + a_2 m_1^2 + a_1 m_1 + a_0 = 0$$

which has closed form solution.

## Net Model: compute R's and C's

R1, and R2 are computed from m1 and m2 with C1 + C2 =

C\_total

R1

R2

$$\begin{cases} -R_{1}(C_{1} + C_{2} + C_{L}) - R_{2}(C_{2} + C_{L}) = m_{1} \\ -R_{1}R_{2}C_{1}(C_{2} + C_{L}) + m_{1}^{2} = m_{2} \end{cases}$$

(4)

• In the absence of positive solutions for R's and C's, solve the Least Square problem.

min

$$[m_1 + R_1(C_1 + C_2 + C_L) + R_2(C_2 + C_L)]^2 + [m_2 + R_1R_2C_1(C_2 + C_L) - m_1^2]^2$$

s. t.  $R_1, R_2, C_1, C_2 > 0$

### Gate Delay/Slew Based on Net Model

• Find new Ceff based on net model

Figure 3: gate driving ceff or net delay model

#### **Extension to Current Source Model**

- Modifications to handle CSM

- The interconnect net models are derived from the initial timing results of CSM reference timer.

- For the receiver model, the average of two receiver capacances is used as load cap (CL in Figure 2).

### **Experimental Results**

- The presented method is implemented in our inhouse tool.

- Benchmarked 4 design blocks

Number of Gates: 35K ~ 730K

Number of Nets: 36K ~ 789K

Technology Node: TSMC 20nm.

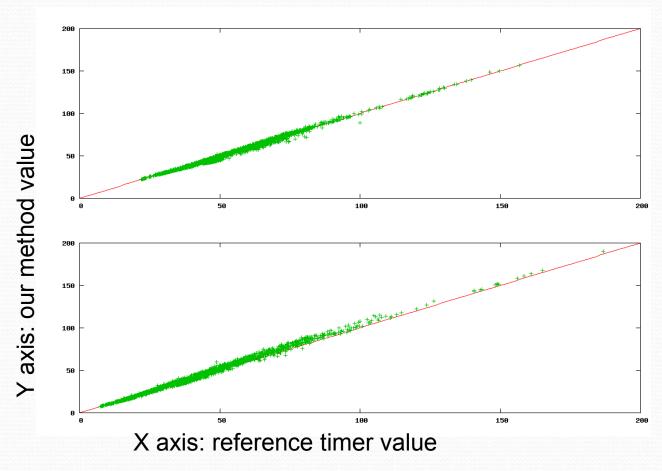

## Figure 4: NLDM delays and slews of net correlation with reference timer

Top: net delay comparison between reference timer and our method bottom: net slew comparison between reference timer and our method

## Figure 5: NLDM delays and slews of gate correlation with reference timer

Top: gate delay comparison between reference timer and our method bottom: gate slew comparison between reference timer and our method

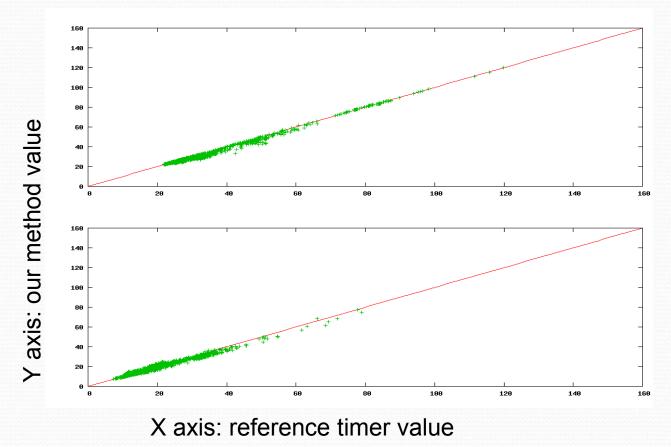

#### Figure 6: NLDM delay and slew error distribution for nets

axis: count

X axis: Error (ps) vs reference timer

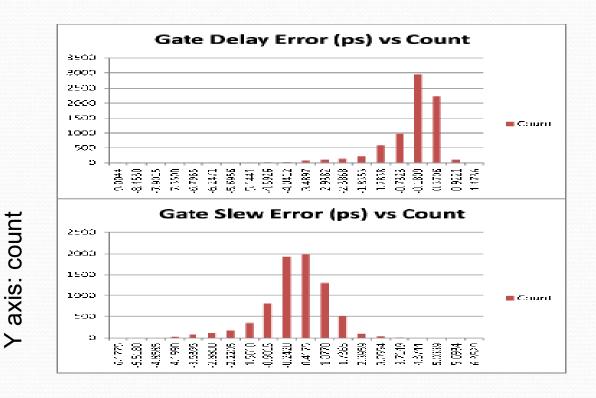

# Figure 7: NLDM delay and slew error distribution for gates

X axis: Error (ps) vs reference timer

Table 1: average and max diff. of NLDM delays and slews w. r. t. reference timer, and memory save.

| desi<br>gns |                  | net delay      |               | net slew       |               | gate delay     |               | gate slew      |              | Mem<br>w/o   | Mem<br>save |

|-------------|------------------|----------------|---------------|----------------|---------------|----------------|---------------|----------------|--------------|--------------|-------------|

|             | Ave.<br>diff(ps) | Max<br>diff(%) | Ave. diff(ps) | Max<br>diff(%) | Ave. diff(ps) | Max<br>diff(%) | Ave. diff(ps) | Max<br>diff(%) | Para<br>(MB) | Para<br>(MB) | (%)         |

| dı          | 0.523            | 8.39           | 0.415         | 10.44          | -0.535        | 9.98           | 0.537         | 17.85          | 1060         | 447          | 57.8%       |

| d2          | 0.0342           | 9.75           | 0.229         | 14.31          | 0.435         | 12.19          | 0.151         | 17.01          | 5739         | 836          | 85.4%       |

| d3          | 0.736            | 8.82           | 0.964         | 15.74          | 0.931         | 14.33          | 0.43          | 19.90          | 2823         | 1108         | 60.8%       |

| d4          | -0.0247          | 9.99           | 0.953         | 16.42          | -0.298        | 16.45          | -0.0211       | 19.81          | 4234         | 1452         | 65.7%       |

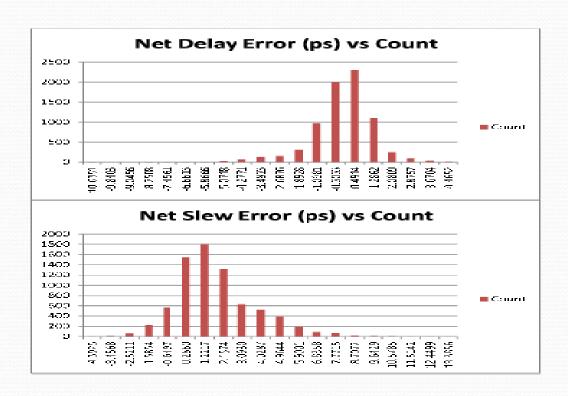

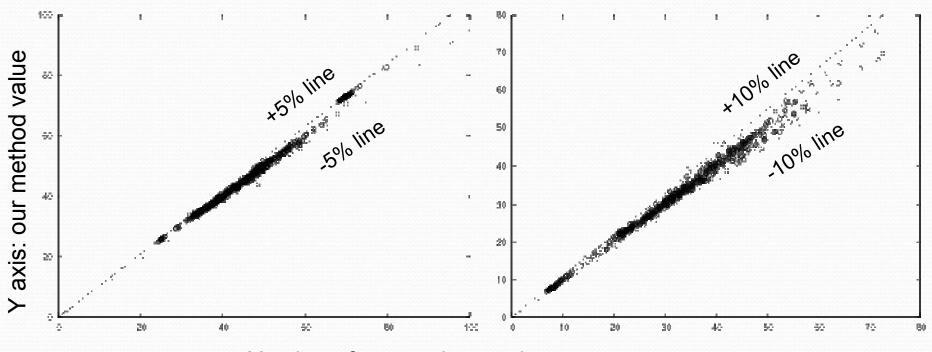

## Figure 8: CSM stage delays and slews of net and gate correlation with reference timer

X axis: reference timer value

Left: stage delay comparison between referene timer and our method. Most are within +-5% lines

Right: gate slew comparison between reference timer and our method. Most are within +-10% lines

#### Conclusion

- A new approach to estimate delay and slew without explicit parasitic data is presented and implemented.

- Excellent accuracy with this fast computation method has been established by qualifying on many designs and comparing the timing results with reference timer.

#### References

- [1] L. T. Pillage, R. A. Rohrer, Asymptotic waveform evaluation for timing analysis, IEEE Transactions on CAD, pp. 352 366, Vol. 9, No. 4, 1990.

- [2] C. L. Ratzlaff, L. T. Pillage, RICE: rapid interconnect circuit evaluation using AWE, IEEE Trans. on CAD of Integrated Circuits and Systems, 1994, Vol. 13, No. 1, pp. 763-776.

- [3] R. W. Freund, P. Feldmann, Reduced-Order modeling of large passive linear circuits by means of the SyPVL algorithm, IEEE/ACM International Conference on Computer-Aided Design, 1996, pp. 280 287.

- [4] A. Odabasioglu, M. Celik, L.T. Pileggi, PRIMA: passive reduced-order interconnect macromodeling algorithm, IEEE Transactions on CAD, pp. 645-654, Vol. 17, No. 8, 1998.

- [5] C. J. Alpert, A. Devgan, and C. V. Kashyap, RC Delay Metrics for Performance Optimization, IEEE Transactions on CAD, Vol. 20, No. 5, 2001.

- [6] C. V. Kashyap, C. J. Alpert, F. Liu, and A. Devgan, Closed-Form Expressions for Extending Step Delay and Slew Metrics to Ramp Inputs for RC Trees, IEEE Transactions on CAD, Vol. 23, No. 4, 2004.

- [7] K. Agarwal, D. Sylvester D. Blaauw, Simple Metrics for Slew Rate of RC Circuits Based on Two Circuit Moments, DAC 2003.

- [8] J. Qian, S. Pullela, and L. Pillage, Modeling the "Effective Capacitance" for the RC Interconnect of CMOS Gates, IEEE Transactions on CAD, Vol. 13, No. 12, 1994.

- [9] F. Dartu, N. Menezes, and L. Pileggi, Performance Computation for Pre-Characterized CMOS gates with RC loads, IEEE Transactions on CAD, Vol. 15, No. 5, 1996.

## Acknowledgement

- Richard Cheung

- Marat Shnur

- Prashant Kabra

- Robert Chung

- Prathyusha Lingambhotla

- Jimmy Cheng

- Bing Shi